Samsung wird nächstes Jahr mit der Massenproduktion von 3nm-Chips beginnen

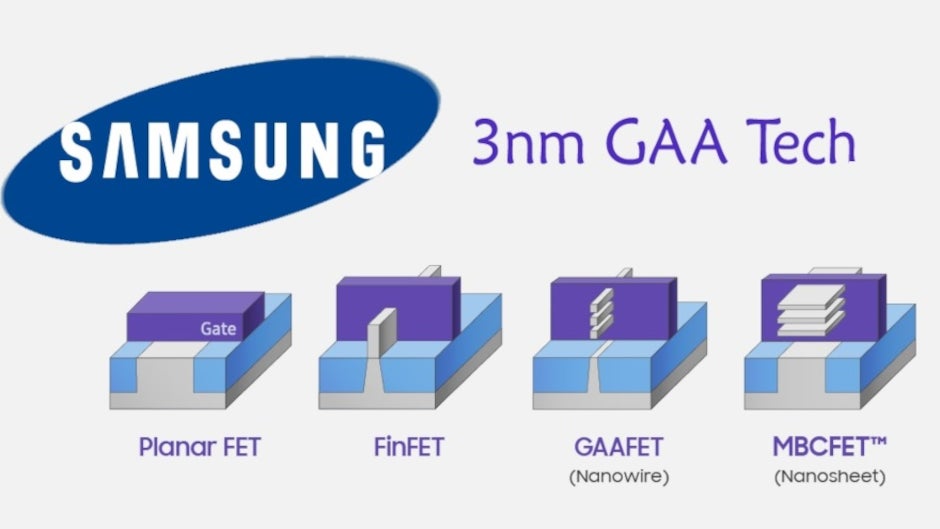

Samsung Foundry, nach TSMC die zweitgrößte unabhängige Foundry weltweit, hat laut Angaben an seinem 3nm-Prozessknoten einige Änderungen vorgenommen Anand Tech. Die ersten im 3nm-Verfahren hergestellten Chips von Samsung Foundry, 3GAE (3nm Gate-All-Around Early), werden ein Jahr später als üblich in Serie gefertigt. Außerdem wurde aus der Roadmap von Samsung entfernt, dass 3GAE nur für den internen Gebrauch produziert werden darf.

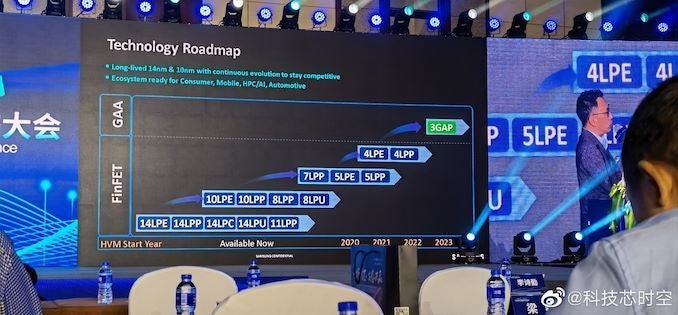

„Für den 3GAE-Prozess haben wir mit Kunden gesprochen und erwarten die Massenproduktion von 3GAE im Jahr 2022“, sagte ein Samsung-Vertreter. Der Nachfolger von 3GAE, der 3GAP-Knoten (3nm Gate-All-Around Plus), steht noch auf der Roadmap, da die Volumenfertigung voraussichtlich im Jahr 2023 beginnen wird. Die obige Roadmap wurde auf dem Foundry Forum 2021 in China vorgestellt. Samsung Foundry stellte ihre aktualisierte technische Roadmap zur Verfügung, die dann auf Baidu und Weibo erneut veröffentlicht wurde.

Bei Chips, die die Legacy-FinFET-Transistorarchitektur verwenden, hat Samsung seiner Roadmap 5LPP und 4LPP mit einer großen Fertigungscharge für 2021 bzw. 2022 hinzugefügt. wann Samsung Es stellte seine 3GAE- und 3GAP-Knoten im Mai 2019 vor und kündigte an, dass es im Vergleich zum 7LPP, der derzeit ein Prozessknoten der vorherigen Generation ist, eine Leistungssteigerung von 35 % und eine Reduzierung des Stromverbrauchs um 50 % bieten wird.

Gleichzeitig wurde 2019 der Produktionsstart mit 3GAA (Gate All-Around Transistor Architecture) für Ende 2021 angekündigt. Mit dem neuen Launch-Termin 2022 für das 3nm Gate-All-Around Early-Verfahren kann man daraus schließen, dass dort ist eine leichte Verzögerung seitens Samsung oder eine Fehleinschätzung. Wie auch immer, es ist keine große Sache, da die frühen Knoten von Sammy von den Herstellern nicht in großem Umfang verwendet werden.

Erst vor wenigen Tagen hat Samsung Foundry einen 3-nm-Chip registriert, der die Gate-All-Around (GAA) Transistorarchitektur verwendet. Das Auswerfen eines Chips ist die letzte Aktion seines Designzyklus, die zu einem von zwei Ergebnissen führt: Das Chipdesign funktioniert oder funktioniert nicht. Im letzteren Fall kann eine kleinere Überholung oder eine größere Konstruktionsüberholung erforderlich sein.

„Lebenslanger Social-Media-Liebhaber. Fällt oft hin. Schöpfer. Leidenschaftlicher Feinschmecker. Entdecker. Typischer Unruhestifter.“